what is phase change memory(PCRAM)?

Phase change memory(pcram) is a type of memory that stores data by altering the state of matter from which the device is fabricated. It can exist in two states amorphous and crystalline phase. These are reversible structural phrases. PCRAM, also known as PCM has fast read access time, good data retention and high data density. Several major memory manufacturers like Samsung, micron has already made a prototype with the implementation of PCM memory implementation.

Architecture of PCRAM

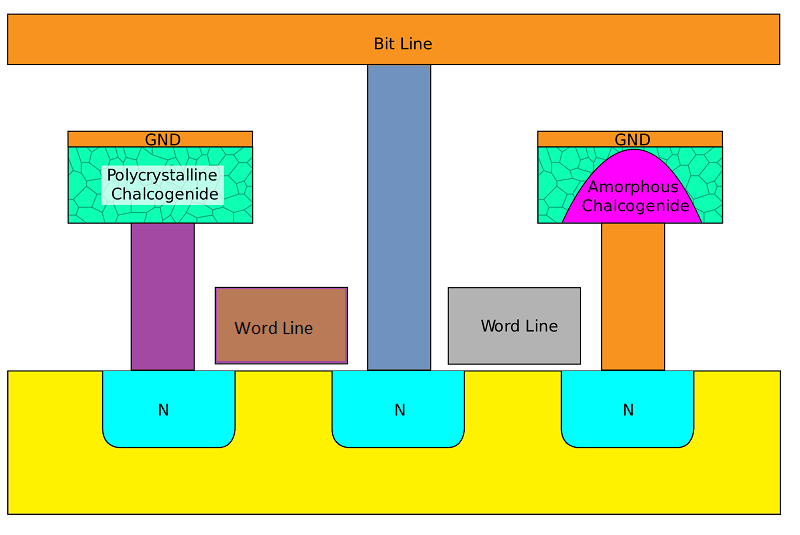

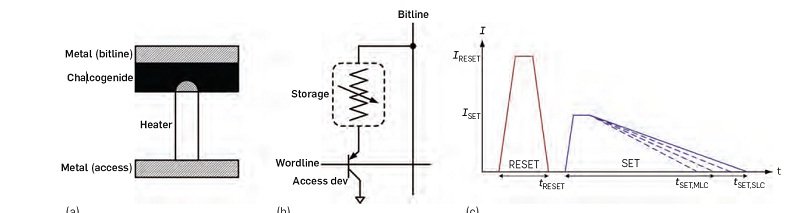

The architecture of PCM has a phase changing material and a narrow electrode called the heater. Between the two electrodes, chalcogenide is commonly used phase changing material. When Chalcogenide is heated and cooled slowly, it retains its amorphous state. In this state, it is highly resistive. This state represents the logic zero. When it is heated and cooled rapidly it becomes crystalline. In this state, it is less resistive and this state represents the logic 1. Write operation is performed by SET or RESET to write the logical 1 or 0 to the memory cell.

In SET operation long moderately powered electrical pulse is supplied and in RESET operation a short high powered pulse is applied. Before the cell is READ the bit line is precharged to the read voltage. The word line is active low when using a BJT active transistor. If a selected cell is in a crystalline state the bit line is discharged with the current flowing through the storage element and the access transistor otherwise the cell is in an amorphous state preventing or limiting the bit line current.

Limitation of PCRAM

Even with all these advantages this technology over DRAM, it could not be implemented over large scale due to its various limitations.

The PCM has limited write endurance of 10^9 to 10^12 cycles. The write speed is also very slow. If these limitations are reduced the DRAM technology can be replaced with PCRAM. In past few years, researchers have proposed several techniques and hybrid architecture with PCM to reduce its limitation.

Hybrid Technology of PCRAM

-

PCM and STT-RAM Hybrid

The hybrid technology is made possible with the spin torque transfer ram and the PCM. The small capacity of STT-RAM is used as a WRITE buffer with a PCM based cache. This Hybrid cache reduces the endurance limitation of PRAM cache by redirecting the WRITE traffic from an upper memory layer to the spin torque transfer ram WRITE buffer. The STT-RAM has virtually no WRITE limitation. However, the STT-RAM has a lower density than PCRAM. So from the combination of the advantages of these two RAM benefits each other. The high WRITE endurance of STT-RAM and the high density of PRAM together increases the lifetime of PCRAM by redirecting the WRITE traffic towards STT-RAM. The technique used is that when there is a data to be written to the PCM, the new data is complied with the old data and the WRITE is triggered when the content of the cells are not matching. This was further improved by using an inverse bit, so if the number of bits to be written is more than half, the WRITE is triggered after inversing the data to be written.

-

PCRAM and DRAM Hybrid.

Another hybrid architecture that uses a small amount of DRAM together with PRAM makes an efficient memory. This hybrid technology has been widely accepted. While PRAM consumes low READ and Sand by power DRAM consumes low WRITE power and provide WRITE endurance. The challenge in design is that the wear leveling of PRAM pages must be managed efficiently to ensure it’s longer lifetime. The hardware part is in the memory controller and manages the access information to different PRAM pages. The software portion is the part of the operating system “the memory manager” which reduces the wear leveling by page swapping. The memory controller is aware of the partitioning of the system memory between PRAM and DRAM. Based on the accessed address, it is able to route a request to the correct memory. The memory controller keeps the map of a number of WRITE access to it. This information is maintained and when the numbers of WRITE accessed the given threshold to any PRAM page then the controller triggers a page swap interrupt to the processor and issues the page address. The operating system then uses the page manager to perform the page swap operations.

Both this hybrid architecture reduces the limitation of PCRAM and increases the efficiency.

Techniques to improve PCRAM Limitations.

Various techniques are used to improve the performance of PCM by decreasing its limitation. Let’s see some of the proposed techniques.

- Enhancing PCRAM efficiency for video application by an approximate WRITE.

- Reducing read latency by using Early Read and Turbo Read.

- OptiPCM Implementation with Photonics.

- PCM Architecture using 3D Die-Stacking.

- Journaling File-System for PCM.

- Exploring Time and Write-back Aware PCM system.

PCM as a Secure Memory

The non-volatile characteristics of PCRAM make a serious threat to computer privacy. Several techniques were explored to increase the security of PCM were proposed to sustain the malicious attack which overwrites the limited number of memory cells by which physical memory is destroyed. Some of these techniques are addressed below.

-

The counter-mode encryption scheme.

This measure was used for privacy protection where the encryption reduces the effect in a significantly for some previously proposed techniques for wear leveling of PCRAM.

-

Maintaining PCMA(Phase Change Memory Address)

In order to prevent a malicious user, to attack some memory cells by overwriting, the computer manipulated the physical address was changed as the PCM memory address. This avoids any malicious user to overwrite PCM memory.

-

Hardware Mechanism.

A low-cost hardware mechanism was proposed called security refresh which works by dynamically randomizing the data address and obfuscating actual address.

-

Multi-way Security Refresh.

Security refresh combined with multi-way wear leveling called multi-way security refresh achieves equal or better lifetime than original two level security refresh.